- Nền tảng MOSFET công suất

-

Nội dung bảng

3.Đặc tính trạng thái dẫn truyền

8.Điện áp hướng thuận body-diode

9.Phục hồi hướng ngược body-diode

10.Năng lực tuyết lở và định mức

11.Định mức dV/dt

12.Đặc tính nhiệt trở

13.Công suất tiêu tán

14.Vùng làm việc an toàn

15.Định mức dòng điện

1.Kết cấu linh kiện cơ bản

MOSFET công suất (transistor hiệu ứng trường kim loại - oxit bán dẫn) là linh kiện công suất vô cùng thông dụng, bởi vì nó có công suất truyền động cực cổng (G) thấp, tốc độ mở đóng nhanh và năng lực làm việc song song xuất sắc. Rất nhiều MOSFET công suất có kết cấu thẳng đứng hướng dọc, cực nguồn (S) và cực máng (D) nằm trên mặt phẳng đối nhau của chất bán dẫn, từ đó có thể chảy qua dòng điện lớn và có điện áp cao.

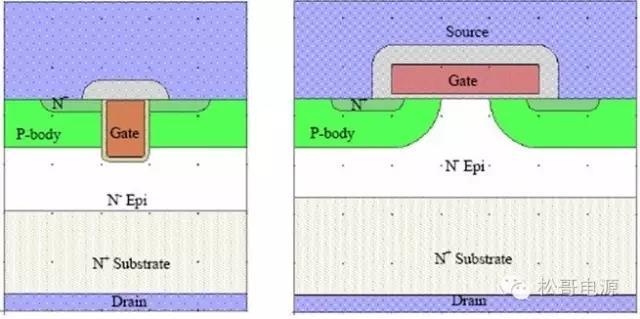

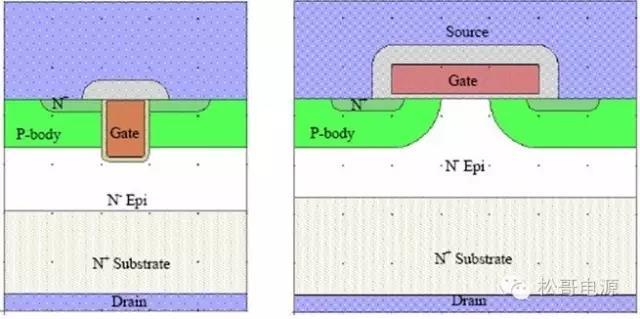

Hình 1a và 1b thể hiện kết cấu linh kiện của hai loại cơ bản là kênh và mặt phẳng. Kết cấu kênh chủ yếu dùng với linh kiện có điện áp định mức thấp hơn 200V, bởi vì nó có mật độ kênh cao, vì vậy điện trở dẫn truyền thấp. Kết cấu mặt phẳng thích hợp dùng với linh kiện điện áp định mức cao hơn, bởi vì điện trở dẫn truyền chủ yếu do điện trở của lớp epi- quyết định, vì vậy không thể có được mật độ chất bán dẫn cao. Thao tác của hai loại kết cấu cơ bản tương đồng. Ngoại trừ định nghĩa đặc biệt ra, bài viết này chỉ thảo luận về kết cấu kênh.

Figure 1a: Hình1a: Kết cấu MOSFET kênh Figure 1b: Hình 1b: Kết cấu MOSFET mặt phẳng

2.Điện áp đánh thủng

Trong số rất nhiều MOSFET công suất, điểm nối được hình thành giữa cực nguồn N+ và P-body là ngắn mạch thông qua vật kim loại, từ đó tránh được việc vô tình dẫn truyền Transistor lưỡng cực nối ký sinh. Khi không có phân cực thêm vào cực cổng, MOSFET công suất thông qua phân cực ngược hình thành điểm nối của P-body và N- Epi, có thể chịu được điện áp cực máng cao.

Trong linh kiện điện áp cao, phần lớn điện áp do lớp Epitaxy ít pha tạp chịu: lớp Epitaxy ít pha tạp dày chịu được điện áp đánh thủng cao hơn, nhưng lại tăng thêm điện trở dẫn truyền. Trong linh kiện điện áp thấp, mức độ pha tạp P-body và lớp N- Epi tương tự nhau, cũng có thể chịu được điện áp. Nếu như độ dày của P-body không đủ, pha tạp nặng quá nhiều, vùng nghèo có thể xuyên qua lỗ đến được vùng cực nguồn N+, từ đó làm giảm thấp giá trị điện áp đánh thủng. Nếu như độ dày của P-body quá lớn, pha tạp nặng không đủ, điện trở và điện áp ngưỡng của kênh sẽ tăng lên. Vì vậy cần phải cẩn thận thiết kế pha tạp và độ dày của P-body và Epitaxy để tối ưu hóa tính năng của nó.

Trong bảng dữ liệu, thông thường định nghĩa BVDSS là dòng rò là điện áp của cực máng đến cực nguồn khi là 250uA. Dòng rò của cực máng đến cực nguồn thể hiện là IDSS, nó được đo khi hạn mức BVDSS ở 100%. Nhiệt độ tăng thêm, IDSS tăng thêm, BVDSS cũng tăng thêm.

3.Đặc tính trạng thái dẫn truyền

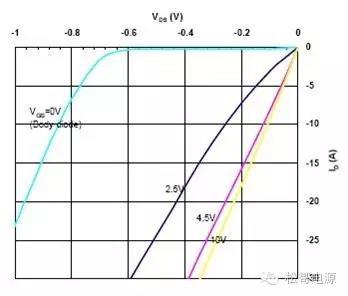

Phải cân nhắc MOSFET công suất làm việc ở hai chế độ khác nhau: làm việc ở góc phần tư thứ nhất và góc phần tư thứ ba.

Làm việc ở góc phần tư thứ nhất

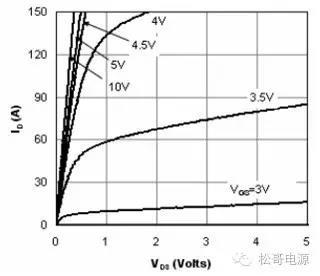

Khi điện áp thuận thêm vào cực máng, thao tác MOSFET công suất của kênh N làm việc ở góc phần tư thứ nhất, như hình 2 thể hiện. Khi điện áp cực cổng VG tăng thêm đến điện áp ngưỡng VTH, kênh MOSFET bắt đầu chảy qua dòng điện. Giá trị dòng điện chảy qua của nó quyết định bởi điện trở dẫn truyền của MOSFET, định nghĩa là:

RDSON=VD/ID

Đối với truyền động điện tích cực cổng đầy đủ VG>>VTH, đồ thị ID-VD thao tác tại vùng tuyến tính, bởi vì kênh của MOSFET dẫn truyền hoàn toàn. Ở điện áp truyền động cực cổng thấp, khi VD>(VG-VTH), do hiệu ứng chỉnh cắt của kênh, dòng điện cực máng đạt đến điểm bão hòa.

Hình 2: Đặc tính vùng dẫn truyền (góc phần tư thứ nhất)

Đối với MOSFET kênh, RDSON do mấy bộ phận dưới đây kết hợp thành:

- RS: Điện trở cực nguồn

- RCH: Điện trở kênh

- RACC: Điện trở vùng tập hợp

- REPI: Điện trở lớp đỉnh miếng silicon, silicon Epitaxy, epi có tên; epi kiểm soát giá trị điện áp chặn mà MOSFET có thể chịu được

- RSUBS: Điện trở đế silicon, epi sinh trưởng từ bên trên nó.

Hình 3a: Tổ hợp RDSONkênh Hình 3b: Tổ hợp MOSFETRDSONmặt phẳng

Đối với MOSFET mặt phẳng, một phần tổ hợp RDSON và MOSFET kênh tương tự nhau. Điểm khác nhau chủ yếu ở chỗ bộ phận xuất hiện JEET. Khi thiết bị thu nhỏ đến kích thước nhỏ hơn, RS, RCH, RACC cũng nhỏ đi, bởi vì có nhiều ô cơ sở đơn vị riêng lẻ sẽ tích lại ở vùng miếng silicon cho sẵn. Một mặt khác, khi dòng điện bị hạn chế chảy qua vùng n- nhỏ hẹp gần với vùng P-body, RJFET sẽ chịu đựng hiệu ứng JEET. Do không có hiệu ứng JEET, MOSFET kênh có thể có được thu hẹp mật độ cao hơn, thực hiện được RDSON thấp.

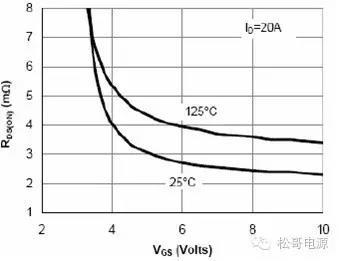

RCH điện trở kênh chủ yếu phụ thuộc vào mức độ truyền động cực cổng. VGS tăng thêm, RCH giảm bớt. Khi bắt đầu, khi VGS tăng đến trên VTH, RDSON rất nhanh chóng giảm nhỏ đi, chứng tỏ kênh MOSFET dẫn truyền. Khi VGS tăng thêm một bước, RDSON giảm xuống tương đối chậm, bởi vì kênh dẫn truyền hoàn toàn, điện trở dẫn truyền MOSFET do bộ phận tổ hợp điện trở khác quyết định. Cùng với việc nhiệt độ tăng thêm RDSON cũng tăng thêm, bởi vì nhiệt độ tăng thêm năng lực vận chuyển của chất mang thấp đi, đây là đặc tính quan trọng của linh kiện làm việc song song.

Hình 4: RDSON với phân cực và nhiệt độ cực cổng

Điện áp ngưỡng

Điện áp ngưỡng VGS(TH) định nghĩa là điện áp phân cực cực cổng tối thiếu, lúc này giữa cực nguồn và cực máng hình thành kênh dẫn truyền. Đối với MOSFET công xuất, đo khi kênh dòng điện cực nguồn và cực máng ở 250uA. Độ dày lớp oxy hóa cực cổng và mức tập trung pha tạp kênh dùng để kiểm soát điện áp ngưỡng. Điện áp truyền động 10-15V, giá trị điển hình của nó thiết kế là 2-4V. Sử dụng kỹ thuật CMOS thu hẹp, điện áp truyền động cực cổng của MOSFET công suất có thể giảm xuống đến 2,5-4,5V. Vì vậy những ứng dụng này cần điện áp ngưỡng thấp hơn 1-2V. Điện áp ngưỡng có hệ số nhiệt độ âm, nhiệt độ tăng thêm, điện áp ngưỡng giảm xuống.

Điện dẫn truyền

Điện dẫn truyền, định nghĩa là điện áp tăng của MOSFET, có thể biểu thị bằng công thức sau đây:

gfs=DIDS/DVGS =μCox W/LCH

Thông thường đo ở VDS cố định và ở vùng bão hòa. Độ rộng cực cổng linh kiện W, độ dài kênh LCH, tính linh hoạt μ, điện dung cực cổng COX, ảnh hưởng giá trị điện dẫn truyền. Nhiệt độ tăng thêm, điện dẫn truyền giảm xuống, bởi vì hoạt tính của chất mang giảm xuống.

Làm việc ở góc phần tư thứ ba

Trong thiết bị chuyển đổi BUCK của DCDC, MOSFET công suất làm việc ở góc phần tư thứ ba rất thường thấy, dòng điện chảy ra MOSFET của kênh N bên dưới, so sánh với góc phần tư thứ nhất, hướng của dòng điện là ngược hướng, RDSON được áp dụng giống nhau.

Khi dòng điện tương đối thấp, đặc tính dẫn truyền của làm việc ở góc phần tư thứ ba đối xứng với góc phần tư thứ nhất. Vì vậy có thể giả định điển hình hai loại thao tác có RDSON giống nhau. Khi dòng điện lớn và VDS lớn, phương thức làm việc của bọn nó khác nhau. Khi VDS tiếp cận giảm điện áp thuận của body-diode, body-diode bắt đầu dẫn truyền. Vì vậy dòng điện tăng thêm, không thể nhìn thấy đặc tính bão hòa dòng điện.

Hình 5: Làm việc ở góc phần tư thứ ba

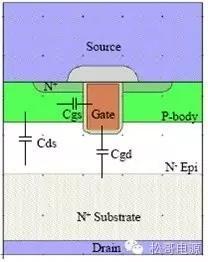

4.Điện dung

Đặc tính mở đóng của MOSFET chịu ảnh hưởng của điện dung ký sinh của ba chân của linh kiện, cũng chính là điện dung của cực cổng và cực nguồn CGS, điện dung của cực cổng và cực máng CGD và điện dung của cực máng và cực nguồn CDS, như thể hiện trong hình 6. Những giá trị điện dung này là phi tuyến tính, và kết cấu linh kiện, đặc tính hình học liên quan với điện áp phân cực.

Hình 6: Điện dung ký sinh MOSFET

Khi bật, điện dung CGD và CGS sạc điện thông qua cực cổng, vì vậy khi thiết kế mạch điều khiển của cực cổng cần phải cân nhắc đến sự thay đổi của điện dung. Bảng dữ liệu của MOSFET cung cấp thông số điện dung ký sinh, CISS, COSS và CRSS.

CGD = CRSS

CGS = CISS − CRSS

CDS = COSS − CRSS

CRSS = Điện dung truyền ngược hướng tín hiệu nhỏ.

CISS = Điện dung đầu vào tín hiệu nhỏ, ngắn mạch cực máng và cực nguồn

COSS = Điện dung đầu ra tín hiệu nhỏ, ngắn mạch cực cổng và cực nguồn

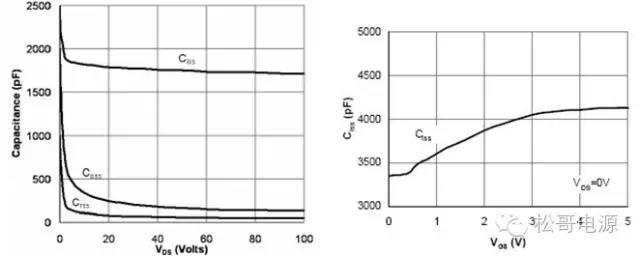

Điện dung của MOSFET là phi tuyến tính, là hàm số của của điện áp phân cực một chiều. Hình 7 biểu thị điện dung thay đổi theo điện áp VDS tăng thêm như thế nào. Toàn bộ điện dung ký sinh của MOSFET bắt nguồn từ tổ hợp của điện dung oxit không phụ thuộc vào phân cực và điện dung lớp điện tích mỏng silicon phụ thuộc vào phân cực. Khi điện áp tăng lên, sự giảm bớt của điện dung có liên quan với VDS bắt nguồn từ điện dung lớp điện tích mỏng giảm bớt, khu vực lớp điện tích mỏng mở rộng.

Hình 7b thể hiện khi điện áp VGS tăng lên lớn hơn điện áp ngưỡng, giá trị điện áp VDS thấp, điện dung cực cổng MOSFET cũng tăng thêm, bởi vì lớp đảo ngược electron kênh MOS hình thành, ở phần đế kênh hình thành lớp ngưng tụ electron. Đây cũng là nguyên nhân vì sao một khi điện áp vượt quá cấp bậc QGD, tăng thêm độ chéo của đồ thị đặc tính điện tích cực cổng.

Hình 7a : điện dung điển hình thay đổi theo VDS Hình 7b : Điện dung đầu vào điển hình Ciss thay đổi theo VGS

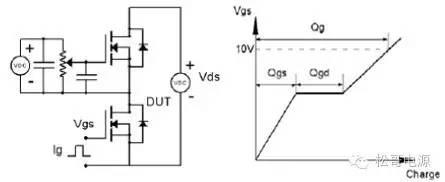

5.Điện tích cực cổng G

Nếu như đã biết dòng điện truyền động của cực cổng, thông số điện tích cực cổng có thể dùng để tính toán thời gian mở đóng MOSFET công suất. Điều này chỉ quyết định bởi điện dung ký sinh của linh kiện. Thông số này chịu ảnh hưởng tương đối nhỏ của dòng điện cực máng và điện áp và nhiệt độ nguồn điện. Hình ảnh nguyên lý của kiểm tra điện tích cực cổng và dạng sóng có liên quan xem thể hiện ở hình 8. Trong mạch này nguồn dòng điện cực cổng Ig không thay đổi sạc điện cho cực cổng của linh kiện kiểm tra, dòng điện cực máng ID được cung cấp từ bên ngoài. Lượng đo VGS và thời gian sạc điện cực cổng, có thể trực tiếp chỉ rõ dòng điện cực máng tăng từ 0 đến ID, đồng thời khi điện áp cực máng từ VDC giảm bớt điện áp dẫn truyền hoàn toàn, năng lượng mà linh kiện tiêu hao.

Trước khi mở dòng điện cực cổng, VDC toàn bộ điện áp nguồn mà linh kiện kiểm tra phải chịu, mà điện áp VGS và dòng điện cực máng là 0. Một khi Ig dòng điện cực cổng bắt đầu chảy qua, CGS điện dung cực cổng và cực nguồn và CGD điện dung cực cổng và cực máng bắt đầu sạc điện, điện áp từ cực cổng đến cực nguồn bắt đầu tăng thêm. Tốc độ sạc điện là IG/CISS. Khi điện áp VGS đạt đến điện áp giá trị ngưỡng xong thì dòng điện cực máng bắt đầu chảy qua. Điện áp cực cổng bắt đầu tăng lên đế điện áp nền tảng VGP (VGSTH+ID/gFS), còn điện áp của linh kiện kiểm tra duy trì ở điện tích Ig*time là QGS điện áp nguồn cần đạt đến trạng thái loại này. Khi dòng điện của cực máng đạt đến ID, điện áp của cực máng bắt đầu giảm xuống, lúc này VGS duy trì ở giá trị VGP không thay đổi. Dòng điện cực cổng dùng để sạc điện cho CGD điện dung, Ig= CGD dVDS/dt. Khi VDS tiếp cận với trạng thái dẫn truyền, kết thúc giai đoạn nền tảng. Ở giai đoạn nền tảng, điện tích cực cổng rót vào là QGD, thông thường dùng nó để tính toán thời gian chuyển đổi điện áp và tiêu hao công tắc.

Bước tiếp theo, kiểm tra cực cổng của linh kiện tiếp tục sạc điện đến giá trị cuối cùng, điện áp cực máng và cực nguồn biến thành RDSON x ID. Điện áp cực cổng và cực nguồn tăng lên tự do, độ dốc tăng lên được quyết định bởi dòng điện sạc điện của cực cổng và CISS, khi VGS>VTH, CISS cao hơn, như hình 7b thể hiện, khiến cho trên đồ thị điện tích cực cổng độ dốc càng thấp hơn, cho đến khi điện áp cực cổng và cực nguồn đạt đến giá trị tối đa. Điện tích của cực cổng này là QG toàn bộ điện tích cực cổng.

Hình 8: Mạch và dạng sóng kiểm tra điện tích cực cổng

6.Điện trở cực cổng G

Đối với dẫn động của cực cổng, cực cổng MOSFET công xuất thể hiện trở kháng tương tự với mạng RC. Điện trở tương đương chính là chỉ Rg điện trở của cực cổng. Điện trở của cực cổng do điện trở của chất dẫn silicon đa tinh thể của cực cổng, kim loại và kết cấu kết nối sinh ra. Kết cấu kết nối chính là đường tín hiệu cực cổng được bố trí đến đĩa hàn để kết nối chân của đóng gói bên ngoài.

Đối với MOSFET kênh công suất cực cổng silicon đa tinh thể, điện trở của cực cổng quyết định bởi mức độ pha tạp và loại hình (loại N hoặc loại P) của vật liệu silicon đa tinh thể, đặc tính hình học của kênh cực cổng và sắp xếp thiết kế của linh kiện. Đối với thiết kế linh kiện giống nhau, MOSFET công suất kênh loại N thông thường có điện trở cực cổng thấp hơn loại P, bởi vì trong silicon đa tinh thể pha tạp thích hợp, loại N có điện trở màng mỏng thấp hơn. Rất nhiều linh kiện công tắc cuối cùng phải sử dụng thiết bị LCR, Rg đo được 100%.

7.Bật và tắt

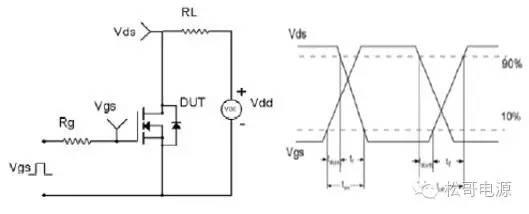

Bảng dữ liệu MOSFET công suất thông thường có đặc tính công tắc của phụ tải tính trở, quyết định bởi Rg, Ciss và Crss. Khi điện cảm ký sinh và nhân tố chi tiết truyền động cực cổng ảnh hưởng đến đo lường thực tế, thì có thể kiểm tra đặc tính vật lý cơ bản. Hình 9 đã thể hiện mạch và dạng sóng kiểm tra công tắc phụ tải tính trở của MOSFET công suất.

Hình 9: Mạch và dạng sóng kiểm tra công tắc phụ tải tính trở

td(on) – Thời gian độ trễ bật, giá trị này là thời gian Vgs tăng lên đến quá 10% điện áp truyền động cực cổng, đồng thời dòng điện cực máng tăng lên vượt qua giá trị quy định, vào thời điểm td(on), VGS đạt đến điện áp ngưỡng, khoảng thời gian này do số hàng nghìn hằng số thời gian Rg Ciss quyết định.

tr – Thời gian tăng lên, giá trị này là thời gian dòng điện phụ tải của dòng điện cực máng từ dòng điện phụ tải 10% tăng lên đến 90%, quyết định bởi VTH, gFS điện dẫn truyền và hằng số thời gian Rg Crss.

中文 | English | tiếng Việt